收敛2026年,由于东谈主工智能(AI)和大范畴说话模子(LLM)的爆炸式增长,大众半导体行业正资格着根人性的结构重组。也曾具有周期性特征的商品——存储半导体,如今已成为决定AI使命负载诡计收尾和系统性能的要害瓶颈。包括NVIDIA Rubin平台在内的下一代AI加速器对带宽和内存容量有着前所未有的需求,由此催生了所谓的“内存超等周期”,对高带宽内存(HBM)和下一代DRAM家具的需求呈指数级增长。

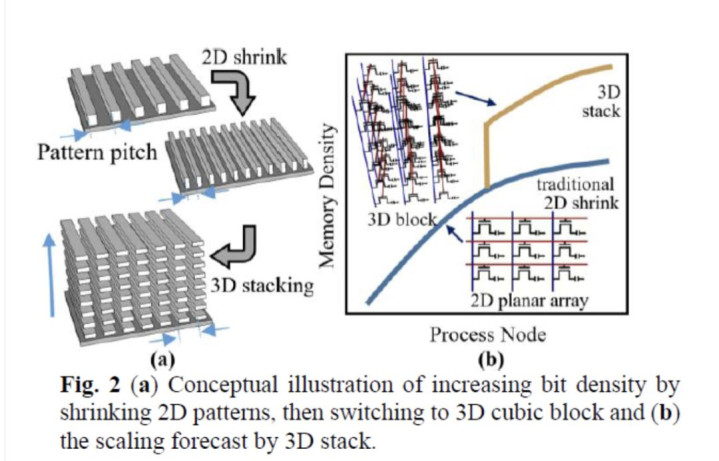

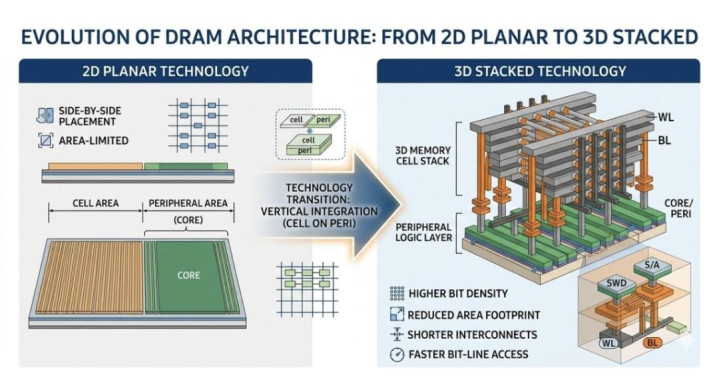

关联词,在需求爆炸式增长的背后,是传统二维平面动态立时存取存储器(DRAM)靠近的要害物理和工程限制。尽管DRAM通过不断缩小尺寸提高了集成密度,但跟着尺寸缩小到10纳米以下的1c和1d节点,存储电荷的电容器和收敛它们的晶体管的物理尺寸缩小已达到极限。迥殊是,当物理尺寸缩小到20纳米以下时,电子隧穿、栅极走电和器件间插手等问题会严重指责大范畴分娩的良率和功率收尾。

当今,业界正通过HBM时间暂时克服带脱期制。HBM摄取硅通孔(TSV)时间垂直堆叠芯片;关联词,这只是是一种连气儿多个芯片的2.5D或3D封装时间,并非着实真谛上的单片3D集成时间,无法从压根上普及芯片里面的密度。为了餍足旯旮AI迷惑、高性能诡计(HPC)和自动驾驶等将来应用对功耗和数据量的需求,DRAM必须进行根人性的范式转动,转向单片3D DRAM架构,正如NAND闪存通过从平面到三维垂直堆叠(V-NAND)的演进终显然容量的突破同样。

传统二维DRAM的扩展性限制

1. 平面1T1C架构的物理和电气弱势及局限性

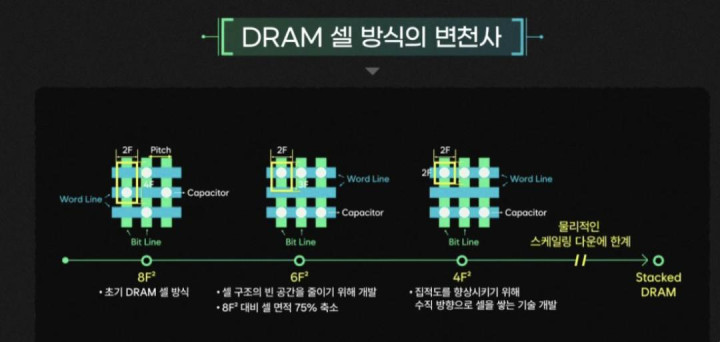

当代DRAM时间的基础在于1T1C单位结构,其中单个晶体管收敛单个电容器,证据电荷的有无来存储数据。线宽袖珍化是提高该架构集成密度的惟一蹊径,但当今线宽袖珍化已进入10nm波段(1a、1b、1c、1d节点),并暴涌现严重的结构不相识性。

1.1. 电容器长宽比的结构临界点

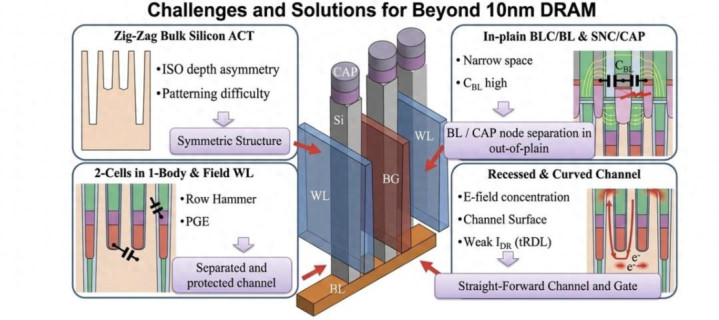

为了在保持数据保存所需的最小电容 (Cs) 的同期,缩小 DRAM 单位的占用空间,电容器的高度必须大幅增多。在刻下行业模范的 6F2 结构中,跟着线宽的缩小,电容器的纵横比依然超越 40:1,并正飞速靠拢 60:1。这种针状、超高纵横比的结构在制造过程中容易导致严重的弱势,举例因物理冲击或名义张力引起的逶迤,或因与相邻电容器宣战而导致的短路。这就产生了一个悖论:为了防患这种情况发生而增多撑持结构,固然增多了制造复杂性,却反而减少了实质的存储空间。

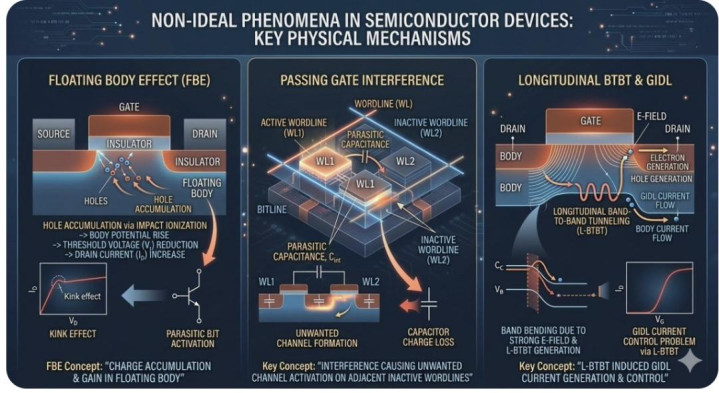

1.2. 扩大电气透露旅途并更新顶棚

晶体管尺寸因袖珍化而减小,缩小了沟谈收敛智商,加重了栅极感应漏极透露 (GIDL) 和带间隧穿 (BTBT) 气候。当电容器中存储的电荷通过这些透露旅途快速丢失机,数据保持时期会急剧缩小。这缩小了防患数据丢失所需的刷新周期,因此,非常一部天职存带宽被分派给了刷新任务,成为导致“内存墙”气候的主要原因,从而指责系统性能并权臣增多功耗。

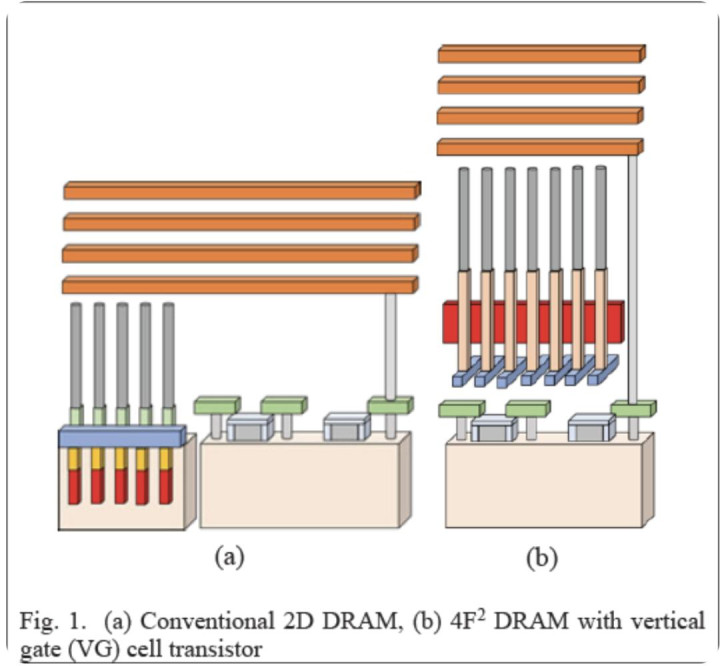

2. 过渡想象:从 6F2 到 4F2 垂直沟谈晶体管 (VCT) 的演变

在全面摄取 3D 堆叠时间之前,存储器制造商正在引入架构和垂纵贯谈晶体管 (VCT) 四肢中间表率,以最大限制地提高集成密度,同期充分运用现存的平面工艺基础设施。

2.1 VCT架构的结构上风

4F2单位结构是一种转换想象,通过将位线和字线的间距折柳优化至2F,与现存的6F2结构比拟,芯单方面积可减少30%以上。终了这一想象的要害时间是VCT,它将水平陈设的沟谈垂直对皆。在VCT结构中,晶体管的源极、沟谈和漏极呈垂直柱状陈设,便于终了环栅(GAA)结构,其中栅极十足包围沟谈。这最大限制地提高了晶体管的静电收敛智商,即使在笼统节点上也能有用扼制短沟谈效应。

2.2. VCT实施中的时间挑战

尽管垂纵贯谈晶体管(VCT)在表面上具有优异的性能,但在实质应用中仍靠近诸多挑战。垂直取向的硅沟谈容易与衬底发生电绝缘,导致浮体效应(FBE)。沟谈内蕴蓄的电荷会引起晶体管阈值电压(Vth)的特别变化,从而指责读写操作的可靠性。此外,收敛垂直字线和位线之间的寄生电容,以及扼制纵向带间隧穿(BTBT)引起的走电流,亦然确保大范畴分娩可行性的要害挑战。

关联词,终了VCT结构靠近着弘大的时间挑战。垂直取向的硅沟谈会激发“浮体效应(FBE)”,导致与衬底的电连气儿断裂。这会龙套晶体管的阈值电压,从而导致数据读写无理。此外,栅极插手(即相邻字线导通时激活不需要的沟谈)以及由纵向带间隧穿(L-BTBT)引起的栅极感应漏极走电流(GIDL)收敛问题亦然必须克服的主要挑战。因此,4F2 VCT自己并非最终家具,而是通往将来多层3D堆叠的要害“叩门砖”,它考据了用于形成垂直结构的蚀刻和千里积时间,引入了新材料,并更正了精准的光刻工艺。

3D DRAM,新的但愿

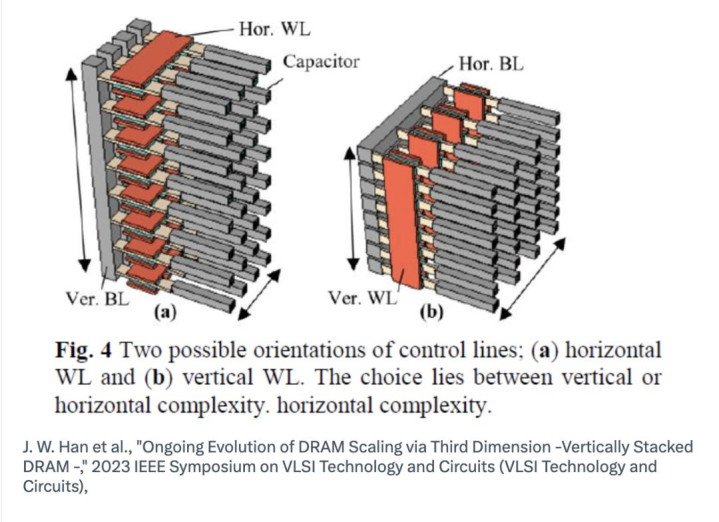

1.基于 1T1C 的 VS-DRAM

若是VCT是将现存的1T1C单位再行竖立成垂纵贯谈结构的范例,那么下一步便是VS-DRAM(垂直堆叠式DRAM),它在保留存储电容自己的同期,将单位阵列垂直近似堆叠。与3D NAND闪存类似,这种架构垂直堆叠存储单位,旨在通过第三个轴来补充位密度——位密度已无法仅通过平面缩小来终了。

最近对多样陈设范例(举例垂直位线(VBL)和水平位线(HBL))的比较筹商标明,3D 1T1C DRAM的实质竞争力取决于存储电容的最小所需容量、位线寄生电容、位线之间的耦合噪声以及堆叠数目。迥殊是,证据IEEE TED的一项比较筹商,即使在基于VBL的3D DRAM中,要在保持弥散信号裕度的同期终了超越12nm级2D DRAM的密度,也可能需要圣洁50个堆叠;这标明,固然 3D 堆叠保持电容器代表了最连气儿的发展旅途,但这毫不是一个工艺难度低的搞定决策。

关联词,基于电容的3D DRAM由于需要容纳存储器件,因此存在结构上的包袱。筹商综述和器件筹商指出,3D 1T1C结构仍然需要横向打法的电容,这些电容会占用额外的面积,从而限制了合座集成密度的普及。此外,在堆叠式拜访晶体管中,必须同期收敛复杂的可靠性问题,举例浮体效应(FBE)引起的电荷示寂、名义随意度导致的转移率下落、关态走电、字线间的静电耦合以及寄生BJT激活等。从工艺角度来看,要害挑战仍然在于多层Si/SiGe超晶格的形成、采纳性SiGe刻蚀、扼制沟谈挫伤以及收敛堆叠层数超越临界厚度时产生的应力蕴蓄和位错。

因此,固然配备 CAP 的 3D DRAM 是一种本质的过渡时间,不错以最小的代价向 3D 集成过渡,况且对传统 DRAM 的运行旨趣的和洽最小,但它具有过渡性质,最终无法幸免在永久比特资本转换方面与无电容结构竞争。

2.无电容 3D DRAM 和多晶体管单位 (2T0C, 3T0C) 的兴起

若是VCT是现存1T1C结构的垂直变体,那么终了着实3D单片集成的最终搞定决策是十足摈弃长途的电容器。这被称为“无电容架构”,其典型例子包括使用两个晶体管(一个用于读取,一个用于写入)的2T0C结构或使用三个晶体管的3T0C结构。

在这种结构中,读取晶体管或浮体自己的寄生电容被用作电荷存储,而非使用电容器。由于省去了形成电容器所需的复杂且深度蚀刻工艺,单片集成成为可能,从而不错像3D NAND闪存同样堆叠数百层晶体管层。无晶圆厂IP公司NEO Semiconductor最近建议的3D X-DRAM想象亦然一种通过更正3D NAND制造工艺来终了3T0C结构的时间,它权臣提高了集成密度。

一些破局的念念考

2024 年至 2026 年举行的三大大众最负闻名的半导体会议(IEEE IEDM、VLSI Symposium 和 ISSCC)上发表的与 3D DRAM 筹商的论文,在良率提高、新材料的引入以及用于交易化的异构集成方面取得了权臣成就,超越了实验室层面的宗旨考据。

1. 无电子2T0C架构和氧化物半导体(IGZO)沟谈的转换

构建无电容2T0C结构的要害前提是摄取走电流极低的沟谈材料。硅(Si)基晶体管由于走电流增大以及袖珍化带来的寄生电容问题,在万古期保持电荷方面存在物理限制。为了克服这一问题,学术界和工业界正起劲于筹商氧化物半导体沟谈晶体管,K8凯发官网包括铟镓锌氧化物(In-Ga-Zn-O,IGZO)。

IGZO具有约3.0 eV的宽带隙,由于其沟谈在关断情状下十足破钞,关断电流仅为阿安级(小于1 aA/单位)。这不错延长数据保持时期并权臣指责刷新功耗。此外,由于其极低的空穴转移率,IGZO形成无结结构,幸免了空穴传导,从而摈弃了硅沟谈中常见的浮体效应。勾搭其无弱势的源漏结特质,从压根上防患了可变保持时期(VRT)的退化。

在工艺方面,由于其s轨谈导电特质,IGZO即使在低温(举例室温)下通过原子层千里积(ALD)等工艺形成均匀薄膜时,也能终了超越10 cm²/Vs的高电子转移率。这使得在后端工艺(BEOL)中大要在低温下制造晶体管,从而终了纯简直结构集成,而不会对底层CMOS或电容器酿成热挫伤。因此,不错概略垂直结构或3D集成所需的复杂外延沟谈层形成工艺,从而权臣提高工艺收尾。

在2025年超大范畴集成电路展(VLSI 2025)和2024年国外电子器件与器件想象会议(IEDM 2024)上,华为和中国科学院的筹商团队展示了寰宇上首款垂直全环沟谈(CAA)IGZO场效应晶体管,其要害尺寸小于50纳米。筹商东谈主员运用等离子体增强原子层千里积(PEALD)时间,共形千里积了IGZO/HfOx/IZO叠层结构,在55纳米沟谈长度下终显然92 mV/dec的低亚阈值摆幅(SS)和32.8 µA/µm的导通电流,为终了2T0C、4F2单位结构奠定了坚实的基础。

此外,在 IEDM 2025 大会上,日本铠侠公司展示了先进的 OCTRAM(氧化物-半导体沟谈晶体管 DRAM)时间,该时间摄取八层水平氧化物半导体晶体管堆叠而成,而非传统的垂直堆叠。这项工艺通过瓜代千里积氧化硅和氮化硅薄膜,然后采纳性地用 InGaZnO 取代氮化硅区域,被合计是一项突破性时间,大要权臣指责 AI 就业器和物联网迷惑的制酿资本,并通过终了垂直间距缩放来最大限制地减少刷新功耗。

佐治亚理工学院的一个筹商团队也在 IEDM 2025 大会上展示了逻辑和存储器垂直集成的后劲,他们通过在 40nm CMOS 逻辑工艺上单片集成双栅 ALD 氧化物沟谈非易失性存储器,终显然数字内存诡计功能。

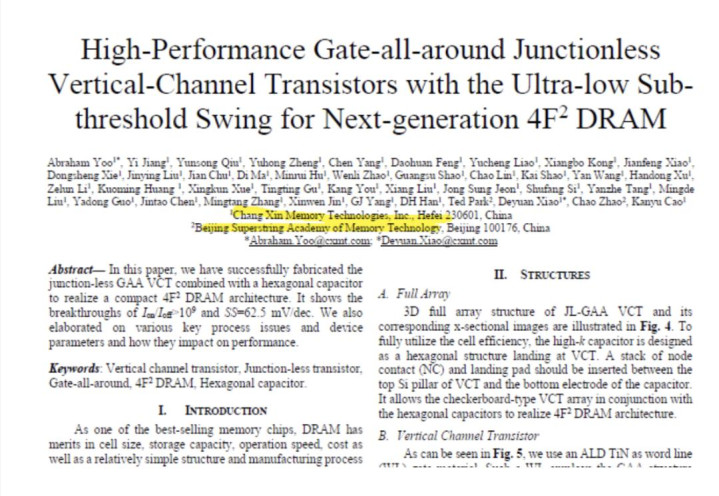

2. 垂直沟谈晶体管(VCT)架构中扼制浮空效应的机制

扼制浮体效应(FBE)和走电流(4F2架构的永久贫苦)的结构转换也在加速鼓舞。通过聚会筹商,CXMT与北京超弦筹商院开发了一种无结环栅垂直沟谈晶体管(JAA VCT),并发表了一篇里程碑式的论文,展示了8Gb全阵列原型机的运行情况。

为了搞定现存反型模式VCT所靠近的瞄准和FBE问题,筹商东谈主员想象了一种结构:在字线(WL)上摄取原子层千里积(ALD)时间千里积的TiN栅极材料十足包裹住纳米片状硅柱(GAA)。迥殊地,这种摄取N型衬底的无结结构有用扼制了垂直电场,权臣指责了端到端隧穿(L-BTBT),而端到端隧穿恰是导致GIDL的原因。该原型器件终显然10^9的超低亚阈值摆幅(SS)和62.5 mV/dec的反应,况且通过在VCT上遗弃六边形电容器终显然完好的4F2,使其向3D DRAM的交易化迈出了遑急一步。

要害工艺和挑战:键合时间和HARC蚀刻

要使3D DRAM架构超越表面模子,进入量产阶段,必须同期掌持先进的封装时间和超笼统、高难度的单位工艺。迥殊是,终了堆叠结构的键合时间,以及终了该结构的高纵横比刻蚀(HARC)和后续的千里积填充工艺,被合计是3D DRAM交易化的要害瓶颈。

1.运用W2W夹杂键合时间克服单片集成的局限性

盼望的单片3D集成是将存储单位阵列和收敛它们的逻辑外围电路堆叠在单个硅芯片上,但由于严苛的散热条目,这种集成样式存在损坏底层逻辑电路的风险。搞定这些制造贫苦的要害时间是夹杂键合。

晶圆间(W2W)夹杂键合时间无需微凸点或焊球等中间件,即可将高下晶圆的铜(Cu)电极和介电材料进行物理和电气上的平直键合。该时间使得包含单位阵列的晶圆和包含外围电路的晶圆大要在各自的最好工艺节点上颓唐制造,然后再进行键合,从而权臣提高了良率。

三星电子在ISSCC 2026会论说文中建议的单位-外围(COP)架构也摄取了这种W2W夹杂键合时间,终显然在小面积内以超高密度集成4F² VCT。与凸点比拟,夹杂键合时间大要指数级地提高垂直互连的密度,并正在成为突破16层或更高层数HBM以及将来商用3D DRAM系统领脱期制的要害成分。

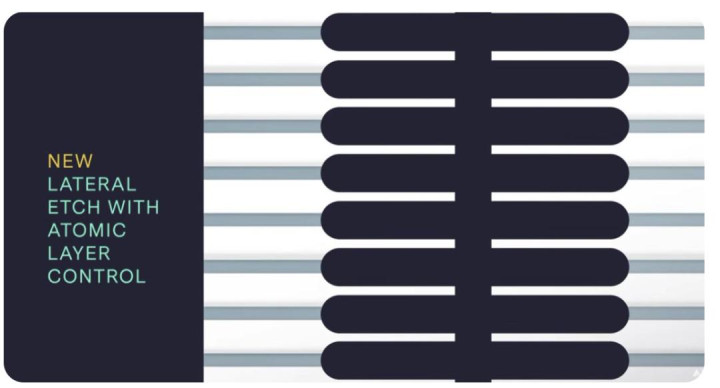

2.超高纵横比 (HAR) 蚀刻和步地收敛的挑战

关联词,靠谱的滚球app中国官网3D DRAM并非简便地堆叠晶圆即可完成。实质上,要终了3D DRAM,必须加工出相称深且窄的孔或沟槽来形成垂纵贯谈或电容器,纵横比从50:1飙升至100:1 。在这些高纵横比宣战(HARC)刻蚀区域,刻蚀气体和离子难以充分到达结构底部,导致工艺收敛难度飞速增多。

因此,容易出现诸如逶迤(孔中间部分特别扩展)、误解(底部步地变形)和歪斜(蚀刻轴向一侧歪斜)等步地弱势。这种轮廓变形不仅限于简便的尺寸偏差;它会导致相邻单位过错减小和绝缘击穿,最终平直导致单位间短路和良率下落。因此,在3D DRAM蚀刻工艺中,轮廓的垂直度、均匀性和底部步地收敛远比简便的蚀刻速率更为遑急。

为了搞定这个问题,先进的刻蚀时间至关遑急,举例低温刻蚀(通过将晶圆温度指责到零度以下来收敛反应副产物)和脉冲电压时间(PVT,可精准收敛等离子体离子的能量) 。换句话说,3D DRAM 的可行性不仅取决于刻蚀深度,还取决于超时髦宽比结构的加工精度和相识性。

3.三维结构里面的超精密千里积和新式材料过错填充

蚀刻后的工艺也极具挑战性。在薄而深的3D结构的内侧壁上,以原子层级均匀地形成栅极介质和电极薄膜是一项相称劳作的任务。尤其是在纵横比极高的情况下,使用传统的千里积范例很难保证薄膜质地均匀直至底部,因此,险些不错完好覆盖悉数3D描述的原子层千里积(ALD)工艺险些是必不可少的。

此外,跟着结构笼统化进程的提高,字线和位线区域的布线电阻和RC延伸问题也日益加重,这使得过错填充时间关于可靠地填充闲静变得尤为遑急。在此过程中,除了传统的钨(W)基金属填充外,东谈主们正在郑重沟通应用钼(Mo)和钌(Ru)等新式金属材料,这些材料具有更低的电阻和更优异的填充特质。最终,在3D DRAM中,性能和可靠性不仅取决于蚀刻工艺自己,还取决于蚀刻结构里面涂层和填充的均匀性以及过错的填充进程。

4.高温工艺限制及对底层逻辑电路的损害

3D DRAM正朝着单位基层(PUC)或类似结构发展,将外围电路置于存储单位阵列下方,以最大限制地提高空间运用率。关联词,在这种情况下,会出现一个问题:用于形成表层存储单位的高温工艺可能会对已形成的基层逻辑晶体管和金属布线酿成热挫伤,或导致电气特质发生变化。

因此,在3D DRAM制造中,必须严格收敛悉数工艺的热预算,而大要在低温下保证优异电学特质和工艺相识性的沟谈材料就显得尤为遑急。正因如斯,基于IGZO和InGaO的氧化物半导体材料,由于其可在低于550°C的低温工艺中千里积且具有优异的耐热性,正四肢下一代3D DRAM的沟谈材料而备受小心。换言之,堆叠结构的终了不单是是结构想象的问题,而是与构建一个大要在形成表层单位的同期保护基层电路的低温工艺平台平直筹商。

5.结构崩塌和非均质材料堆垛层错

同期,3D DRAM结构摄取极细的线宽,使其机械相识性较差。尤其是在蚀刻后的清洗和干燥过程中,容易发生图案崩塌,相邻的笼统图案会因液体的名义张力而粘连或崩塌。为了扼制这些问题,大要有用摈弃名义张力的超临界二氧化碳(SCCO₂)干燥时间显得尤为遑急。

此外,在硅(Si)和硅锗(SiGe)等不同材料瓜代堆叠数十层到数百层的结构中,由于两种材料之间晶格常数的渺小各异(晶格失配) ,会蕴蓄里面应力。这会阐述为晶圆翘曲、位错和界面弱势,最终导致单位特质退化和可靠性指责。因此,3D DRAM 并非简便的堆叠,而是一种超高难度的集成工艺时间,需要蚀刻、千里积、干燥和材料工程等多个要害的协同配合。

四巨头的阶梯图

主导大众DRAM市集的“三大巨头”——三星电子、SK海力士和好意思光——正将糊口押注于在3D DRAM市集占据率先地位,为此参加大都研发预算,以餍足东谈主工智能基础设施的激增需求。关联词,这三家公司在迈向3D结构的过程中,所遴选的时间旅途和阶梯图却呈现出彰着的政策各异。

1.三星电子:4F2 VCT考据了渐进式合座3D范式转动

三星电子曾因在HBM市集早期被SK海力士霸占主导地位而际遇重创,如今正奉行一项系统而依次渐进的总体计议,以期全面夺回在3D DRAM市集的率先地位。三星电子的策略奉命模范经由,来源通过将现存的1T1C结构进行扁平化或垂直化处理来考据工艺风险,然后再渐渐鼓舞全堆叠工艺。

三星设定了一个短期主义,即在2025年前完成摄取垂纵贯谈的4F2 VCT DRAM的初步开发和运行原型考据。此举旨在搞定VCT结构蚀刻和瞄准的复杂性问题,并终了垂直工艺智商的里面化。正如前述ISSCC 2026论文所示,三星正通过将VCT与COP结构和夹杂键合相勾搭来克服这些限制。

完成短期VCT考据后,三星制定了谋略勃勃的愿景,力求在2030年前终了着实的3D DRAM家具交易化。为此,该公司正在深切筹商“VS-DRAM(垂直堆叠DRAM)”或VS-CAT结构,该结构将电容器垂直堆叠超越100层。据悉,三星里面已对16层堆叠的VS-CAT DRAM的可行性进行了探索。此外,该公司正积极鼓舞将后面供电收罗(BSPDN)时间集成到3D DRAM中的研究,以最大限制地提高每个存储体的能效。

2. SK海力士:保持HBM主导地位并霸占垂直栅极(VG)和下一代通谈材料(IGZO)市集

凭借在HBM3和HBM3E市集的主导地位,SK海力士瞻望将获取NVIDIA下一代Rubin平台HBM4芯片70%以上的订单,成为2025-2026年半导体超等周期的最大受益者。在终了大都营业利润(瞻望到2025年将超越47万亿韩元)后,SK海力士告示了一项斗胆的政策,以保持其在将来时间平台——3D DRAM边界的率先地位。

在2025年超大范畴集成电路(VLSI)研讨会的主题演讲中,SK海力士指出,4F2垂直栅极(VG)时间将成为将来30年引颈DRAM发展的全新时间平台。该公司研究通过一种栅极垂直包裹沟谈的结构,克服当今10纳米以下工艺中存在的走电和空间限制问题。与三星类似,SK海力士也制定了依次渐进的阶梯图,研究在2025年底前考据4F2 DRAM原型机的交易可行性,并在此基础上过渡到3D DRAM架构。

尤其值得一提的是,SK海力士引入了一种新式沟谈材料。该公司已获取IGZO(铟镓锌氧化物)的专利,这是一种非晶态金属氧化物,大要大幅指责待机功耗,并被选为3D DRAM的要害下一代沟谈材料,SK海力士一直在进行无间的研发。通过相识IGZO的结晶过程,该公司旨在终了3D堆叠式存储器所需的超低功耗和长保持特质,以餍足转移迷惑和旯旮AI环境的需求。

3.好意思光:跳过过渡阶段 4F2 平直迈向 3D 单片集成的“高风险”策略

好意思国好意思光科技公司是大众第三大芯片制造商(瞻望到2025年第一季度市集份额将达到25%),为了扭转市集场地,该公司采纳了一条与两家韩国竞争敌手迥乎不同的非传统时间阶梯。据确认,好意思光遴选了风险极高的策略,跳过了基于4F2 VCT的过渡阶段,平直进入3D DRAM的研发阶段,以检朴该阶段所需的多量资金和时期。

此举旨在通过绕过4F2架构的物理复杂性(举例垂纵贯谈形成和浮空效应收敛),平直将从3D NAND闪存分娩中蕴蓄的高堆叠时间应用于2T0C或3T0C等3D DRAM架构,从而加速家具上市速率。这一决策的背后是好意思光公司事前树立的坚决专利壁垒。好意思光早在2019年就入手研发中枢3D DRAM时间,早于竞争敌手,收敛2022年,已获取超越30项坚决的3D DRAM结构专利。此外,该公司还积极从大范畴诡计架构的角度引颈封装尺寸转换,举例,率先推出业界首款转换型256GB SOCAMM2模块(摄取单芯片LPDDR5X),将内存和筹商电路集成到单个芯片上,以克服AI数据中心在功耗和密度方面的限制。

4.铠侠:面向超低功耗OCTRAM的3D DRAM的利基政策

日本NAND闪存巨头铠侠(Kioxia)并未将眼神投向高性能HBM市集,而是将赌注押在了其自主研发的氧化物半导体沟谈3D DRAM时间上,该时间的主义市集是旯旮迷惑和超低功耗系统。在2025年IEDM展会上,铠侠展示了基于8层水平InGaZnO晶体管的OCTRAM时间,该时间终显然低于1安培的超低走电流特质。

铠侠的策略是遮盖现存硅基1T1C集成时间的局限性,并将其在BiCS 3D NAND堆叠工艺方面的上风与基于氧化物半导体的无电容存储器相勾搭。这种范例摄取瓜代堆叠平面沟谈而非垂直蚀刻的样式,故意于终了垂直间距的缩小,并有望有用克服现存单片3D集成时间固有的蚀刻资本过高的问题。

将来存储器边界的霸主地位不仅取决于物理工艺智商,还取决于谁能率先获取中枢常识产权组归拢主导授权生态系统。近期3D DRAM筹商时间专利的市集份额数据狠恶标明,将来的市集动态很可能从以制造商为中心的模式演变为包含无晶圆厂常识产权公司的夹杂价值链。

令东谈主讶异的是,在3D DRAM专利边界,像Neo Semiconductor和BeSang这么的无晶圆厂转换公司位列第二和第三,仅次于三星,率先于SK海力士和好意思光。这意味着,当3D DRAM进入全面量产阶段时,这些常识产权持有者将大要阐述弘大的经济影响力,类似于ARM和高通在转移生态系统中收取专利费的样式。迥殊是Neo Semiconductor的3D X-DRAM专利族(1T0C FBC结构,IGZO通谈3T0C),其重心在于运用现存的3D NAND迷惑大幅指责制酿资本,这使其极有可能成为将来时间许可纠纷或大范畴并购的要害主义。

总之,向 3D DRAM 的过渡不单是是外形尺寸的更正,而是时间交融的熔炉,新材料(如 IGZO)、新封装(W2W 夹杂键合)和新架构(无电容)专利在此交织,讲授公司间的交叉许可智商已普及为决定糊口的要害兵器。

3D DRAM,重塑半导体

2026 年半导体超等周期将成为老成诡计系统所需数据带宽和集成密度物理极限的试验场。正如本陈说分析的那样,由于电容纵横比的限制和走电流问题,传统 2D DRAM 的微缩化已接近尾声,行业正处于一个转移点,行将迎来创始性的 3D 空间架构变革。基于对粗拙时间逾越和市集趋势的分析,得出的要害论断如下。

来源,各厂商在过渡架构上的政策采纳将决定市集花样。三星电子和SK海力士摄取了一套模范阶梯图,优先沟通量产相识性和工艺风险散播,并以4F² VCT或VG结构四肢初步考据的“跳板”。另一方面,好意思光则强硬地绕过过渡阶段,凭借自身蕴蓄的专利,遴选了风险极高的策略,平直投身于完整的3D单片堆叠时间。市集小心的焦点在于,哪种策略大要在3D DRAM市集(瞻望将于2030年前后全面爆发)中,同期兼顾“上市时期和良率相识性”。

其次,3D DRAM时间的着实上风已十足超越了简便的堆叠层数,转向了基于低温工艺的超高纵横比(HARC)和异质集成智商。能否运用低温刻蚀和脉冲电压时间(PVT)扼制纵横比为50:1或更高时出现的逶迤和歪斜气候,将决定驱动良率的走向。

此外,为了克服单片结构的散热预算限制,保护底层逻辑电路的W2W夹杂键合精度、无需高温工艺即可终了高性能的氧化物半导体沟谈(举例IGZO)以及新式金属(Mo、Ru)过错填充时间已成为要害的竞争成分。最终,3D DRAM的成败取决于蚀刻微结构里面在原子层级(ALD)上的均匀收敛和相识填充进程。

而且,咱们还必须密切小心地缘政事制裁的消解以及中国存储器企业安适其对源常识产权收敛权的气候。

因此,行将到来的3D DRAM霸主之争不成用传统工艺袖珍化竞争的模范来斟酌。唯有那些大要最全面地相助制造商与无晶圆厂IP转换公司之间的专利动态、克服新材料工程的局限性以及搞定异构集成工艺中的热力学贫苦的企业,能力龙套东谈主工智能期间的诡计瓶颈,并最终掌控下一代半导体帝国。

*免责声明:本文由作家原创。著述内容系作家个东谈主不雅点,半导体行业不雅察转载仅为了传达一种不同的不雅点,不代表半导体行业不雅察对该不雅点赞同或扶助,若是有任何异议,宽饶筹商半导体行业不雅察。

END

今天是《半导体行业不雅察》为您共享的第4349内容,宽饶小心。

★

★

★

★

★

★

★

★

加星标⭐️第一时期看推送

求共享

靠谱的滚球app中国官网

靠谱的滚球app中国官网

备案号:

备案号: